La frequenza di funzionamento dei microprocessori cresce più velocemente rispetto a quella delle memorie. Quando la CPU ordina una richiesta alla memoria centrale deve attendere parecchi cicli di clock prima di essere servita.

Per ridurre l’inattività del microprocessore, dovuta all’attesa per il recupero dei dati dalla memoria centrale, nella CPU è stata implementata la memoria cache. La cache è una memoria piccola e veloce che immagazzina i dati utilizzati più frequentemente in modo da accelerarne l’accesso.

La maggior parte dei programmi, che utilizzano parecchia memoria durante la loro esecuzione, accedono frequentemente agli stessi dati. Una grande percentuale di dati, frequentemente utilizzati, se presenti nella cache riducono di parecchio la latenza della memoria (l’intervallo di tempo che intercorre fra il momento in cui si fa richiesta di input e il momento in cui è disponibile il suo output).

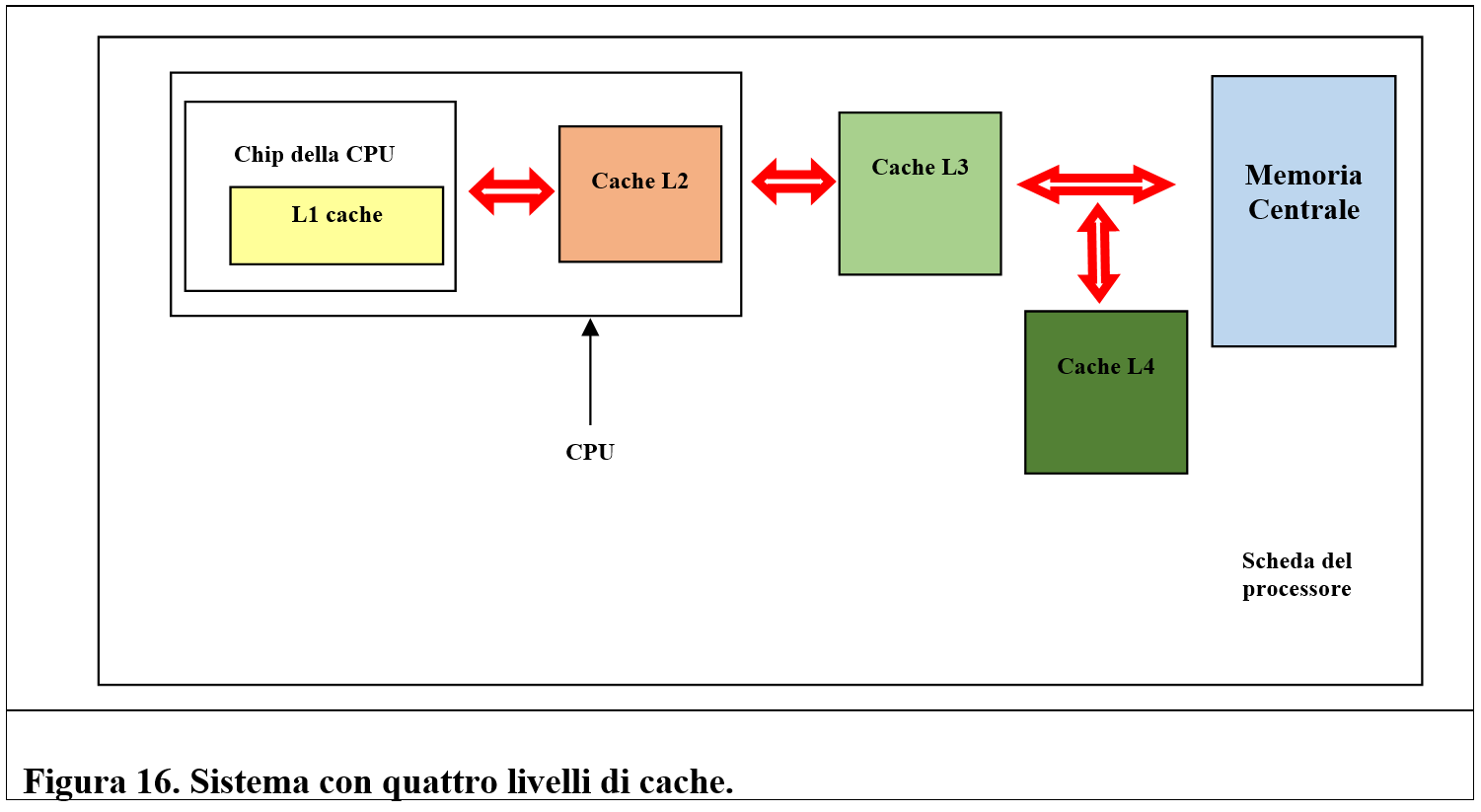

Una delle tecniche per migliorare la velocità di elaborazione delle istruzioni è quella di implementare nel sistema più memorie cache che, insieme, aumentano la larghezza di banda, cioè la quantità di dati fornita per unità di tempo.

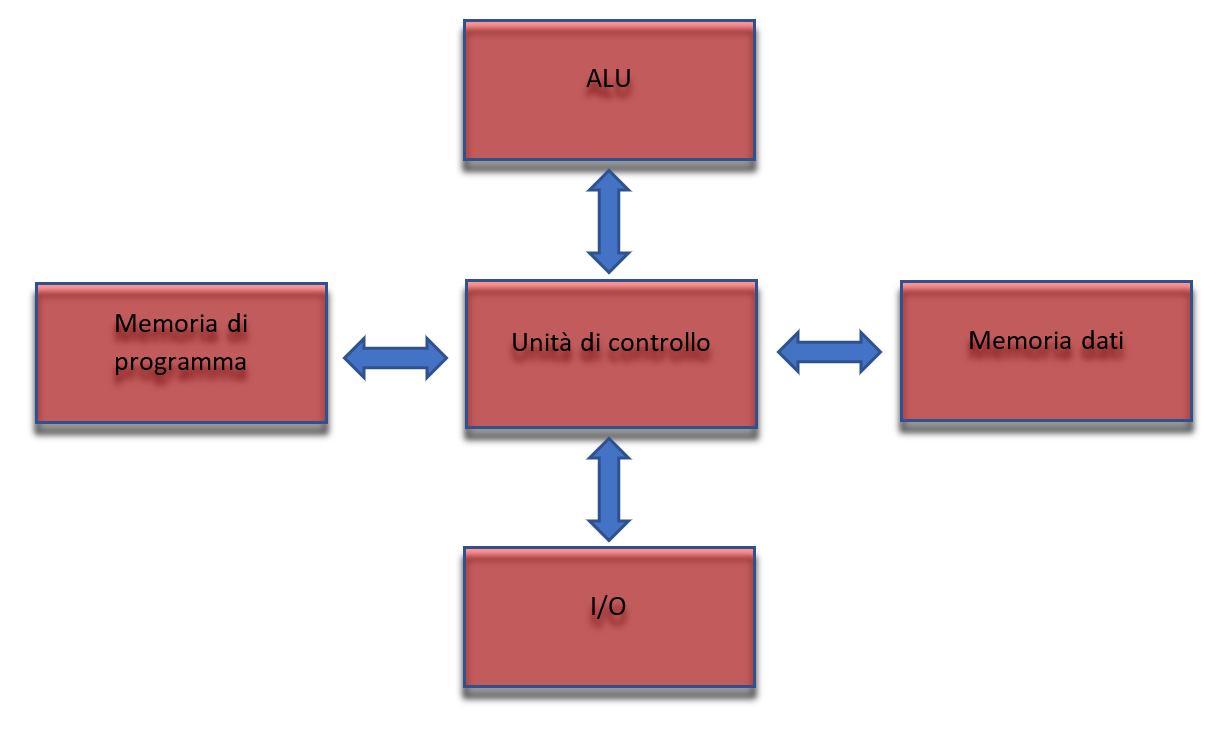

Una ulteriore tecnica consiste nell’implementare due cache separate: una per le istruzioni e una per i dati. Ogni cache ha un accesso indipendente alla memoria centrale. Questa soluzione permette di far partire le operazioni di memoria in modo indipendente per ciascuna cache. Un sistema che adotta questo modello si definisce sistema a cache separata o architettura Harvard, in memoria del calcolatore Mark III di Howard Aiken ultimato nel gennaio del 1943.

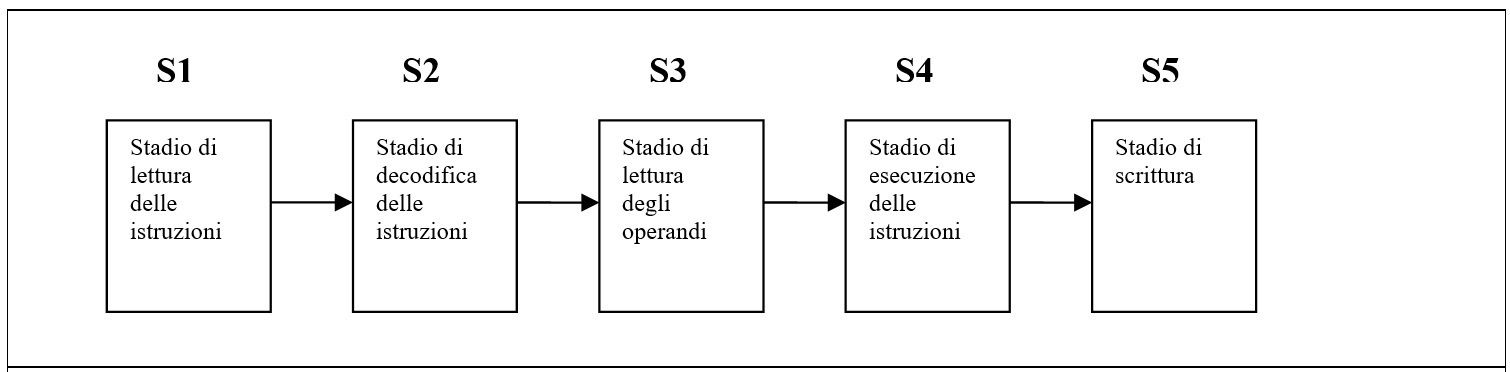

La Pipeline ha apportato ulteriori miglioramenti. Infatti, in una struttura a Pipeline, l’unità di prelievo dell’istruzione richiede l’accesso alle istruzioni; contemporaneamente l’unità di prelievo dell’operando accede ai dati. Questo tipo di accesso parallelo non è possibile in un sistema a cache unificata.

I sistemi moderni adottano, tra la memoria centrale e le cache delle istruzioni e dei dati, una ulteriore memoria veloce: la cache di secondo livello. In realtà, in alcuni sistemi sono presenti ulteriori livelli di cache.

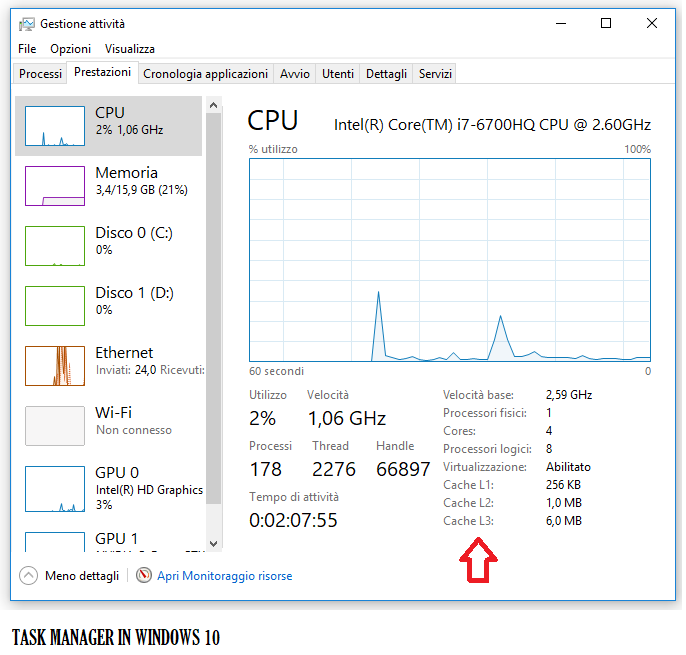

Il chip del microprocessore contiene una cache per le istruzioni e una per i dati di dimensioni comprese tra 8 e 64 Kilobyte. Una cache di secondo livello (cache L2) può essere presente nell’involucro della CPU e collegata al suo chip attraverso circuiti ad alta velocità e contiene solitamente sia dati che istruzioni. La sua dimensione è compresa tra 64 Kilobyte e 8 Megabyte.

È possibile implementare una cache di terzo livello (cache L3), meno veloce dei livelli superiori, sulla scheda del processore. La dimensione della cache L3 può essere di alcuni Megabyte (Range 4MB – 128 MB)

Sommario, Bibliografia e Sitografia

Vincenzo Barile

segue…