Con il termine IA-32 (Intel Architecture – 32) si indica l’architettura dei microprocessori prodotti dalla Intel, dalla AMD (Advanced Micro Devices) e da altre aziende minori per il mercato dei desktop. Il Pentium 4, realizzato dalla Intel, è un esempio.

La IA-32 non è più in grado di accogliere le nuove e sempre più avanzate tecnologie.

L’architettura a 32 bit è stata sostituita, in una prima fase, dal progetto EM64T e, successivamente, dall’architettura IA-64 (Intel Architecture – 64).

L’EM64T non costituisce un’architettura del tutto nuova, ma è una realizzazione tecnica più ampliata del Pentium 4 che risolve il problema dello spazio degli indirizzi. In realtà, si tratta di una estensione dell’architettura a 32 bit capace di indirizzare un quantitativo più ampio di memoria e di eseguire anche applicazioni e sistemi operativi a 64 bit. Questo progetto, nonostante le migliorie tecniche, lascia senza soluzione le problematiche implementative del Pentium 4.

La vera novità è rappresentata dall’architettura IA-64, sviluppata dalla Intel e da Hewlett Packard che si differenzia radicalmente dalla IA-32; infatti permette di realizzare macchine completamente a 64 bit. Itanium è il primo processore che ha implementato IA-64.

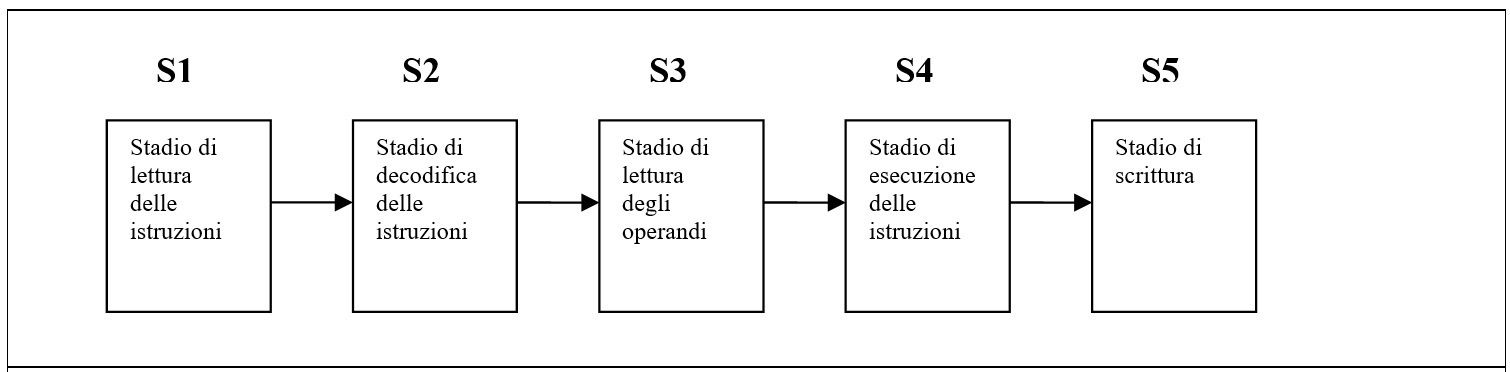

Prima di analizzare i particolari di questa nuova architettura, è importante esaminare i limiti della IA-32. L’architettura IA-32 è basata su una ISA (Instruction Set Architecture, architettura dell’insieme d’istruzioni) ormai obsoleta. Una ISA CISC ha istruzioni di lunghezza variabile difficili e lente da decodificare. L’istruzioni IA-32 possono essere suddivise, in fase di esecuzione, in micro-istruzioni di tipo RISC. Quest’ultime sono di lunghezza costante e più facili da decodificare, ma questo passaggio richiede hardware specifico più complesso e dispendiose risorse temporali. L’architettura della Intel, a 32 bit, implementa un insieme di registri piccoli e irregolari, costringendo a memorizzare i risultati intermedi delle operazioni in memoria. Aumenta, in questo modo, l’accesso alla memoria. Inoltre, disponendo di pochi registri aumentano le dipendenze (soprattutto quelle di tipo WAR) e deve essere necessariamente implementata la tecnica della ridenominazione. Queste problematiche richiedono l’ausilio di numerosi transistor. Tutte queste operazioni sono gestite tramite pipeline con numerosi stadi; ciò comporta maggiori cicli di clock per completare le istruzioni.

L’architettura a 32 bit limita i programmi a 4 Gigabyte di memoria complessiva; problema risolto già con il progetto EM64T.

Tutti questi svantaggi hanno reso indispensabile la realizzazione di un nuovo progetto, necessario soprattutto ai server di fascia alta.

Lo IA-64 cambia la filosofia dell’architettura di base spostando il carico di lavoro dalla fase di esecuzione alla fase di compilazione. È nella fase di compilazione che vengono: riordinate le istruzioni, rinominati i registri, elaborato lo scheduling delle unità funzionali e svolti altri lavori per impiegare tutte le risorse hardware senza generare conflitti.

Per ampliare le prestazioni di un processore, l’architettura a 64 bit introduce numerose funzionalità. Ne analizziamo qualcuna facendo riferimento all’Itanium 2, un processore con architettura interamente a 64 bit.

Uno dei metodi utilizzati per ridurre gli accessi alla memoria è quello di disporre, all’interno della CPU, di una ampia cache di primo livello e di una cache di secondo livello ancora più grande.

L’Itanium 2 dispone di 128 registri di uso generale (64 bit ciascuno), di cui 32 sono di tipo statico e i rimanenti sono utilizzati come registri di stack. Il numero di registri visibili dal programma in esecuzione è variabile. Ogni procedura ha libero accesso ai 32 registri statici più un ad numero variabile di registri allocati in modo dinamico, in base alle reali esigenze di ogni procedura. Inoltre, l’Itanium 2 dispone di 128 registri in virgola mobile, utilizzati anche per memorizzare i risultati intermedi delle operazioni in virgola mobile, 64 registri predicativi ad 1 bit, 8 registri di salto e 128 registri per applicazioni specifiche. Questo approccio ottimizza l’uso dei registri e riduce gli accessi alla memoria.

Una CPU a 64 bit è in grado di scegliere l’ordine di esecuzione delle istruzioni, inclusa l’esecuzione parallela, senza che si generino conflitti.

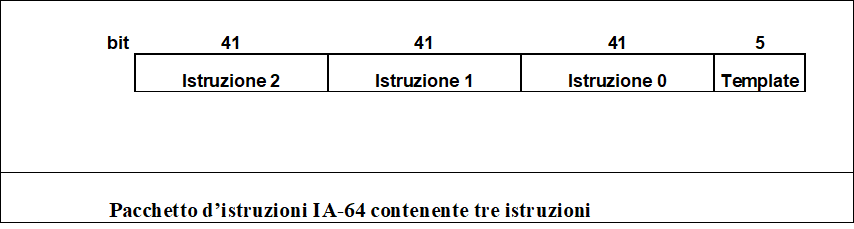

Le istruzioni sono organizzate a pacchetti d’istruzioni di 128 bit. Ogni pacchetto ne ingloba tre di 41 bit e un campo template di 5 bit; quest’ultimo specifica le unità funzionali necessarie al pacchetto, quali le ALU, le operazioni di memoria, le operazioni floating point e i salti.

Sommario, Bibliografia e Sitografia

Vincenzo Barile

segue…