Una prima classificazione dei microprocessori può essere istituita sul tipo di istruzioni implementate del tipo CISC o RISC.

L’architettura CISC, acronimo di Complex Instruction Set Computer (computer con un insieme di istruzioni complesse), implementa un set di istruzioni capaci di eseguire operazioni anche laboriose. Il termine CISC compare con la nascita delle macchine RISC, come termine contrapposto.

I primi microprocessori CISC erano programmati con il linguaggio assembler; ma dagli anni ’70 l’assembler fu sostituito da un linguaggio di programmazione ad alto livello. Il programmatore disponeva di istruzioni complesse che permettevano di generare programmi veloci richiedenti poca memoria, una risorsa costosa negli anni ’60.

I processori CISC integrano un set di istruzioni di lunghezza variabile che permettono di sfruttare nel modo ottimale la memoria disponibile con un numero ridotto di registri. Realizzare i registri era molto costoso, in quanto richiedeva l’utilizzo di molti transistor. Molti registri richiedono molti bit per essere indirizzati e quindi di conseguenza più memoria per l’immagazzinamento delle istruzioni. Il numero ridotto di registri obbliga questi processori ad accedere spesso alla memoria.

Le architetture CISC riducono il divario esistente fra il linguaggio macchina e il linguaggio ad alto livello. Questo non è stato sufficiente per incrementare realmente le prestazioni. Attraverso studi tecnici si è scoperto che una serie di istruzioni semplici rende più efficiente una CPU. Un set di istruzioni complesse rende più ardua l’architettura in quanto richiede l’utilizzo di molto silicio e un numero notevole di transistor, a scapito delle altre unità funzionali.

La famiglia Motorola 68000, l’architettura x86 di Intel e AMD, VAX, PDP-11 sono esempi di sistemi CISC.

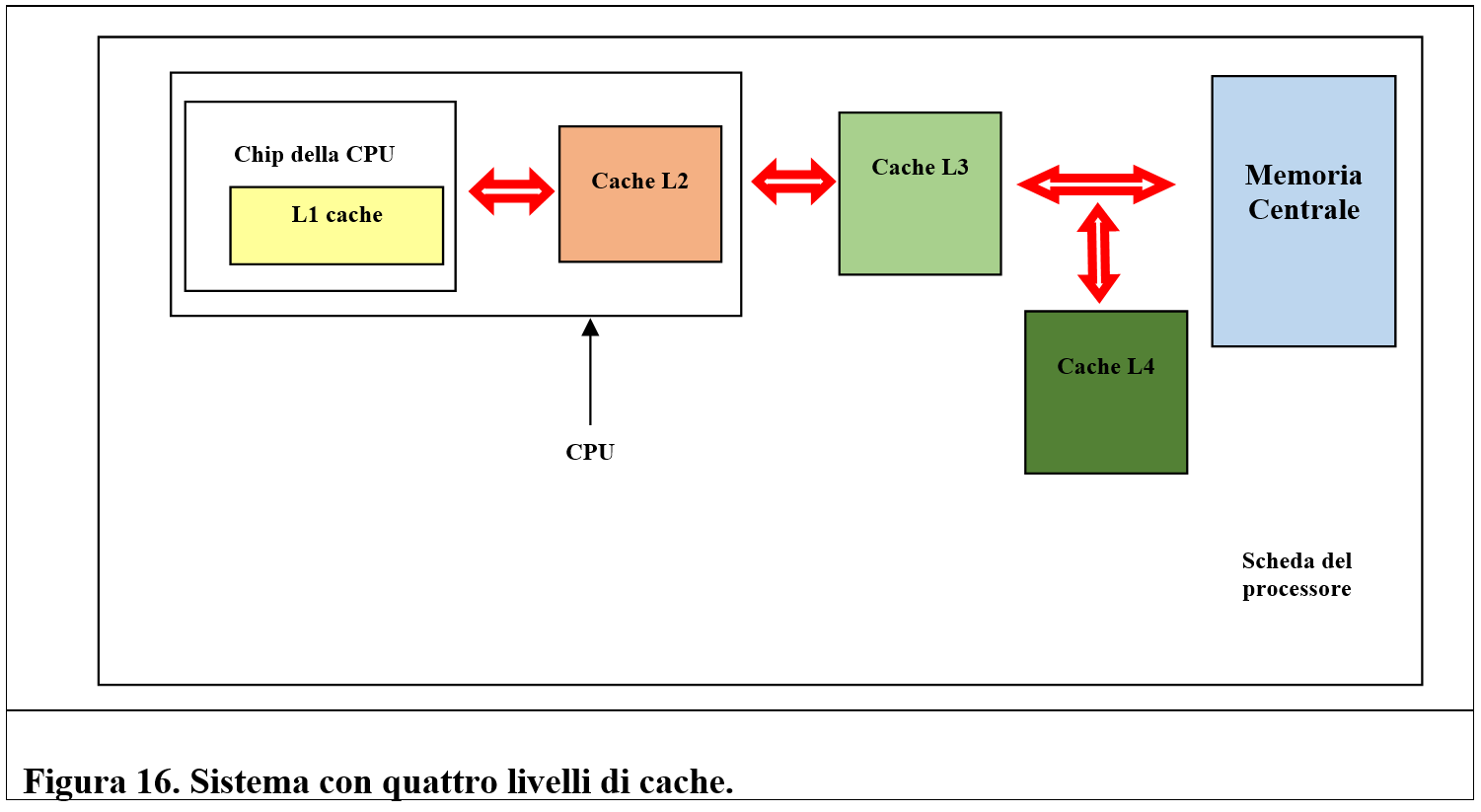

Sul finire degli anni ’70, le CPU e le memorie avevano velocità simili, ma il futuro prevedeva divari sempre più accentuati tra la velocità dei processori e il tempo di accesso alle memorie. Per evitare un calo delle prestazioni, i progettisti pensarono di includere più registri e più cache nella struttura della CPU. Registri e cache richiedevano molto spazio e di conseguenza si ebbe la necessità di recuperarlo riducendo la complessità dei microprocessori.

Le CPU prodotte in quegli anni erano sovradimensionate rispetto alle reali esigenze dei programmi. Le applicazioni richiedono, nella maggior parte del tempo di processo, l’esecuzione di operazioni comuni e molto semplici. I ricercatori si concentrarono su questo tipo di operazioni cercando di rendere la loro esecuzione il più veloce possibile eliminando le istruzioni e i modi di indirizzamento poco usati. L’obiettivo dei ricercatori era quello di ridurre il set di istruzioni rendendolo più compatto. Nascono così i RISC, acronimo di “Reduced Instruction Set Computer” (computer con un set di istruzioni ridotto).

I microprocessori RISC implementano un numero ridotto di istruzioni e di modi di indirizzamento rispetto all’architettura CISC, permettendo di progettare architetture più semplici con l’utilizzo di pochi transistor. I transistor rimanenti sono utilizzati per realizzare molti più registri e per implementare strutture come le pipeline.

Nei processori RISC le istruzioni hanno tutte lo stesso formato e la stessa lunghezza e vengono eseguite in un solo ciclo di clock; nei microprocessori CISC alcune operazioni vengono eseguite in modo rapido (1 o 2 cicli di clock), mentre altre più complesse richiedono decine di cicli di clock, come ad esempio le operazioni di divisione.

L’architettura RISC non è stata progettata per essere programmata in assembler, ma per linguaggi ad alto livello. Opportuni compilatori provvederanno a tradurre le istruzioni in linguaggio macchina.

I processori RISC hanno il grande vantaggio di essere veloci, ma richiedono l’occupazione di parecchia memoria da parte del codice.

Una differenza fondamentale tra RISC e CISC sta nella filosofia di funzionamento. Le operazioni di load e store, in un’architettura RISC, sono le uniche ad accedere alla memoria: tutte le altre utilizzano solo i registri. L’accesso alla memoria può richiedere un tempo considerevole e non prevedibile. Nelle macchine CISC l’accesso ai registri e alla memoria da parte di tutte le operazioni è indifferente, ma non può avvenire direttamente. Se un’operazione richiede l’accesso alla memoria, il processore carica il dato salvandolo in uno dei suoi registri, esegue le operazioni e infine salva il risultato ottenuto in memoria.

I progettisti, all’inizio degli anni ’80, erano convinti che l’architettura dei processori avesse raggiunto il suo limite teorico di velocità. Ma questa convinzione presto venne spazzata via con lo sviluppo di nuove tecnologie, che pur non innalzando la frequenza di funzionamento dei microprocessori, ne migliorano le prestazioni.

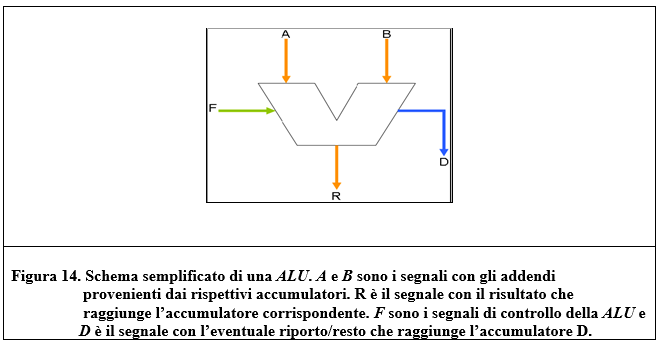

Un’idea brillante fu quella che portò allo sviluppo delle pipeline. Il principio era quello di dividere l’istruzione in sotto-operazioni che venissero svolte in modo sequenziale dalle varie unità funzionali. Prelevare un’istruzione, decodificarla, caricare gli operandi, eseguire l’operazione e salvare il risultato sono fasi che un processore classico esegue in modo sequenziale. Un processore con tecnologia pipeline esegue queste operazioni in parallelo aumentando i tempi di elaborazione.

Studi tecnici dimostrarono come i tempi di elaborazione potessero essere incrementati anche attraverso il lavoro parallelo di più unità funzionali. La replicazione delle unità combinata alla tecnologia della pipeline portarono alla realizzazione di processori superscalari capaci di eseguire in un ciclo di clock più di un’operazione.

Per essere implementate, queste nuove tecnologie richiedevano molti più transistor; i processori RISC risultavano pronti per accoglierle.

Il numero notevole di transistor sui RISC permise notevoli migliorie a questi processori permettendo loro di aumentare il numero di registri disponibili; di incrementare il parallelismo interno e la dimensione della cache; di aggiungere ulteriori funzionalità come la gestione dell’I/O o unità vettoriali SIMD (Single Instruction Multiple Data); offrire risparmio energetico e numerosi altri vantaggi.

Le CPU RISC seguono l’architettura Harvard che permette di dividere il flusso dei dati dal flusso delle istruzioni in modo da consentire ai processori di funzionare senza interruzione ed ottimizzare la gestione della cache.

Il primo sistema che aderì al “progetto RISC” fu il super-computer CDC 6600, sviluppato da Jim Thornton e Seymour Cray nel lontano 1964. Il super-computer aveva una CPU specializzata per eseguire i calcoli e la sua memoria consentiva alle unità load/store di funzionare in parallelo. Una vera bomba di tecnologia.

Nel 1980 fu istituito, sotto la direzione di David Patterson, il progetto Berkeley RISC che mirava ad ottimizzare le prestazioni di una CPU implementando la pipeline e l’uso di molti registri. Il progetto sviluppò il processore RISC-I nell’anno 1982 composto da 44.420 transistor rispetto agli oltre 100.000 utilizzati dai CISC di quell’epoca e dotato di 32 istruzioni. Il RISC-II, suo successore, con soli 40.760 transistor era dotato di 39 istruzioni ed era tre volte più potente; venne utilizzato dalla società Sun Microsystems per sviluppare i processori SPARC.

John Hennessy commercializzò il progetto MIPS. I processori MIPS sono, tuttora, i processori RISC più utilizzati e integrati soprattutto all’interno di console quali la PlayStation (PlayStation, PlayStation 2 e PlayStation Portable) e Nintendo 64.

La IBM sviluppò la piattaforma RS/6000 basata sull’architettura POWER. L’architettura POWER, attraverso un processo di semplificazione, portò alla nascita dei processori PowerPC, utilizzati in applicazioni legate all’automazione. Questa CPU, utilizzata da anni dalla società Apple, è stata inoltre utilizzata nelle sue varianti per la realizzazione di console quali la Nintendo GameCube, dalla Xbox 360 e dalla PlayStation 3. Ci sono altri numerosi progetti che utilizzano processori RISC.

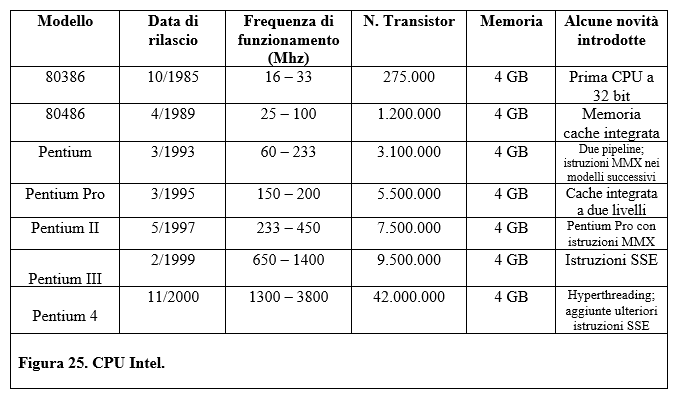

L’architettura x86 prodotta da Intel è oggi la piattaforma di riferimento, nonostante i successi del processore RISC. Questo monopolio di mercato è spiegato dal fatto che gli utenti, a svantaggio di prestazioni più elevate che possono essere ottenute dalle moderne architetture, preferiscono mantenere la compatibilità con le loro applicazioni. L’architettura x86 ha una base utenti talmente ampia da spiazzare il progetto RISC.

Dal processore Pentium Pro dell’Intel, le istruzioni x86 di tipo CISC vengono tradotte internamente in istruzioni RISC che vengono elaborate dalla CPU come un RISC classico. Quest’ultima struttura ibrida è chiamata CRISC. Le istruzioni più complesse dei CISC rendono i programmi compilati più lenti influenzando le prestazioni di un microprocessore. I processori ibridi (CRISC) per effettuare la conversione (da CISC in RISC), implementano alcune tecniche con architetture più sofisticate. L’architettura ibrida è un metodo per aumentare le prestazioni di un microprocessore mantenendo la compatibilità con il sistema CISC, ma non fornisce prestazioni paragonabili ai processori RISC nativi.

Sommario, Bibliografia e Sitografia

Vincenzo Barile

segue…